OpenAI’s ChatGPT App Directory: The New App Store Revolutionizing Chats

Tech News, 19 December, 2025: OpenAI launched the ChatGPT app directory on December 17, 2025, establishing a centralized hub for third-party developers to submit and integrate apps directly into ChatGPT sessions across web, iOS, and Android platforms. This feature streamlines user interactions by enabling seamless app invocation without needing external switches. ChatGPT App: https://chatgpt.com/apps

Key Features: Effortless @Mentions and Tools

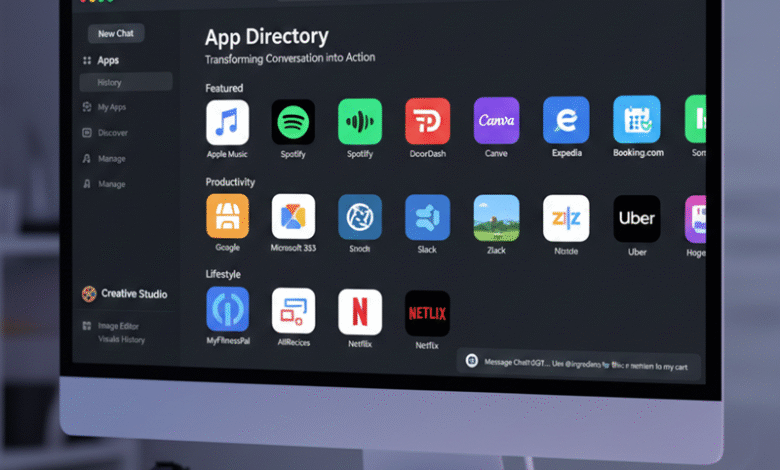

Users activate apps via simple @mentions, such as “@Spotify, create a playlist from my recent likes,” or through a dedicated tools menu, supporting tasks like travel bookings with Booking.com, graphic design in Canva, or music curation via Apple Music. Apps are organized into categories including Featured, Lifestyle (e.g., DoorDash for food orders), and Productivity (e.g., Figma for collaboration, Google Drive for file access), transforming ChatGPT into an all-in-one AI assistant.

Developer Integration and Rollout

Developers build apps using the new Apps SDK and submit them for OpenAI’s rigorous review process, which checks safety, privacy compliance, and functionality before native integration into chats. Initial partners include Spotify, Apple Music, DoorDash, Google Drive, and Figma, with broader submissions opening soon and full deployment slated for early 2026. This creates a competitive “app store” ecosystem within ChatGPT, with potential monetization via developer fees or premium tiers.

Why It Matters

The directory saves users time by keeping everything in-chat, while offering developers fresh opportunities to reach millions. As more apps join, everyday tasks will become faster and more integrated into AI conversations.